삼성전자, 업계 최초 'QLC 9세대 V낸드' 양산

입력 2024.09.12 08:07

수정 2024.09.12 08:08

고용량 QLC·고성능 TLC 통해 차세대 낸드플래시 시장 경쟁력 강화

'채널 홀 에칭' 기술로 더블 스택 구조의 업계 최고 단수 제품 구현

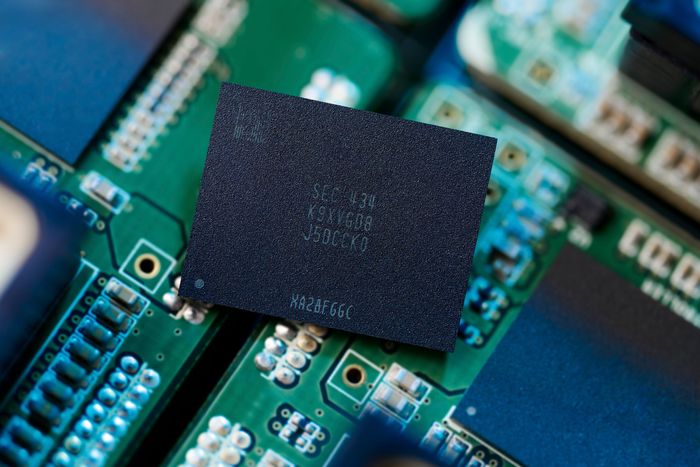

업계 최초 양산, 삼성전자 QLC 9세대 V낸드 제품ⓒ삼성전자

업계 최초 양산, 삼성전자 QLC 9세대 V낸드 제품ⓒ삼성전자

삼성전자는 AI시대 초고용량 서버SSD를 위한 '1Tb(테라비트) QLC(Quad Level Cell) 9세대 V낸드'를 업계 최초로 양산했다고 12일 밝혔다.

1Tb(Terabit) V낸드는 1조 비트의 셀을 단일 칩 안에서 구현한 제품이며 QLC(Quad Level Cell)는 하나의 셀에 4bit 데이터를 기록할 수 있는 구조를 말한다.

삼성전자는 지난 4월 'TLC 9세대 V낸드'를 최초 양산한데 이어 QLC 제품까지 선보이며 고용량∙고성능 낸드플래시 시장 내 입지를 공고히했다. TLC(Triple Level Cell)는 하나의 셀에 3bit 데이터를 기록할 수 있는 구조를 뜻한다.

삼성 9세대 V낸드는 '채널 홀 에칭(Channel Hole Etching)' 기술을 활용해 더블 스택(Double Stack) 구조로 업계 최고 단수를 구현해냈다.

채널 홀 에칭(Channel Hole Etching)은 몰드층을 순차적으로 적층한 다음 한번에 전자가 이동하는 홀(채널 홀)을 만드는 기술이며 더블 스택(Double Stack)은 '채널 홀' 공정을 두 번 진행해 만든 구조다.

이번 QLC 9세대 V낸드는 셀(Cell)과 페리(Peripheral)의 면적을 최소화해 이전 세대 QLC V낸드 대비 약 86% 증가한 업계 최고 수준의 비트 밀도(Bit Density)를 자랑한다.

페리(Peripheral)는 셀의 동작을 관장하는 각종 회로들로 구성된다. 비트 밀도(Bit Density)는 단위 면적당 저장되는 비트(Bit)의 수를 말한다.

V낸드의 적층 단수가 높아질수록 층간, 층별 셀 특성을 균일하게 유지하는 것이 더욱 중요해졌으며, 삼성전자는 이를 위해 '디자인드 몰드(Designed Mold)' 기술을 활용했다. 몰드(Mold)는 셀을 동작시키는 WL(Word Line)의 층이다.

'디자인드 몰드'란 셀 특성 균일화, 최적화를 위해 셀을 동작시키는 WL(Word Line)의 간격을 조절해 적층하는 기술로, 데이터 보존 성능을 이전 제품보다 약 20% 높여 제품 신뢰성을 향상시켰다.

WL(Word Line)는 트랜지스터의 on/off를 담당하는 배선이다.

이번 9세대 QLC는 셀의 상태 변화를 예측하여 불필요한 동작을 최소화하는 '예측 프로그램(Predictive Program) 기술' 혁신을 통해 이전 세대 QLC 제품 대비 쓰기 성능은 100%, 데이터 입출력 속도는 60% 개선했다.

또한 낸드 셀을 구동하는 전압을 낮추고 필요한 BL(Bit Line)만 센싱해 전력 소모를 최소화한 '저전력 설계 기술'을 통해 데이터 읽기, 쓰기 소비 전력도 각각 약 30%, 50% 감소했다.

BL(Bit Line)은 데이터 쓰기, 읽기 역할을 담당하는 배선으로 WL(Word Line)과 함께 Cell Array를 이룬다.

허성회 삼성전자 메모리사업부 Flash개발실 부사장은 "9세대 TLC 양산 4개월 만에 9세대 QLC V낸드 또한 양산에 성공함으로써 AI용 고성능, 고용량 SSD 시장이 요구하는 최신 라인업을 모두 갖췄다"며 "최근 AI향으로 수요가 급증하고 있는 기업용 SSD 시장에서의 리더십이 더욱 부각될 것"이라고 밝혔다.

삼성전자는 브랜드 제품을 시작으로 향후 모바일 UFS, PC 및 서버SSD 등 QLC 9세대 V낸드 기반 제품 응용처를 점차 확대할 계획이다.